Home > Product > Gas turbine system > IC698CHS009 gas turbine electric card

IC698CHS009 gas turbine electric card

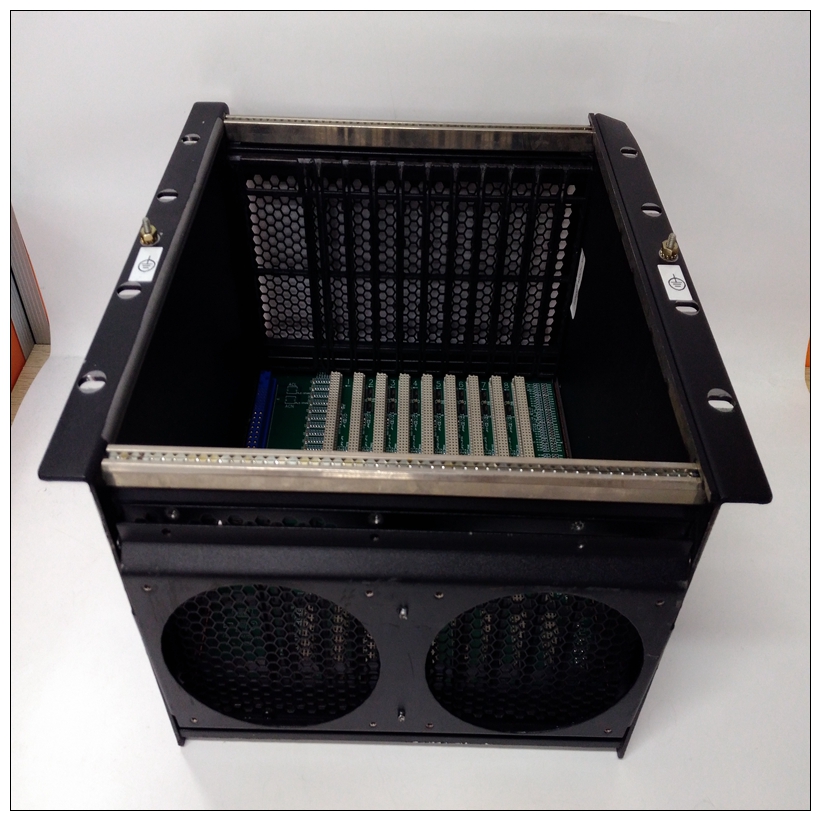

- Product ID: IC698CHS009

- Brand: GE

- Place of origin: the United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:IC698CHS009gas turbine electric card

- Get the latest price:Click to consult

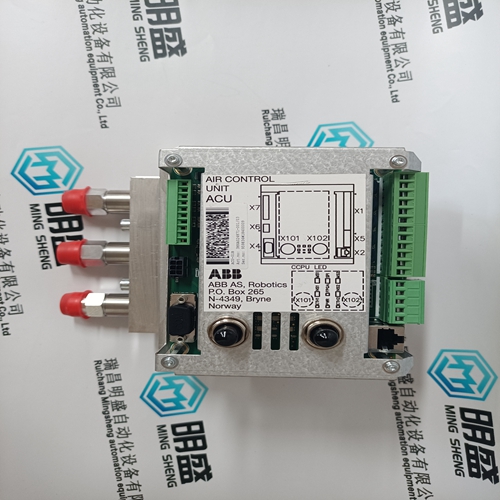

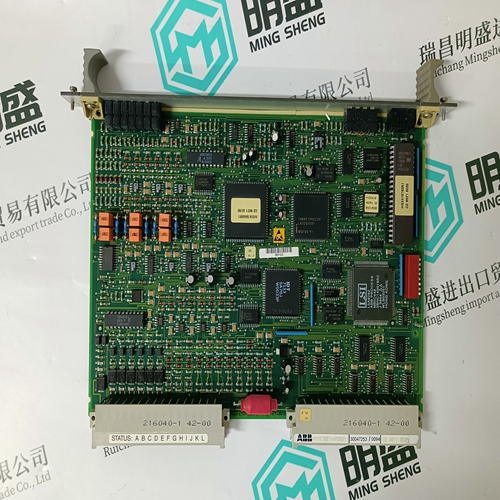

The main products

Spare parts spare parts, the DCS control system of PLC system and the robot system spare parts,Brand advantage: Allen Bradley, BentlyNevada, ABB, Emerson Ovation, Honeywell DCS, Rockwell ICS Triplex, FOXBORO, Schneider PLC, GE Fanuc, Motorola, HIMA, TRICONEX, Prosoft etc. Various kinds of imported industrial parts

Products are widely used in metallurgy, petroleum, glass, aluminum manufacturing, petrochemical industry, coal mine, papermaking, printing, textile printing and dyeing, machinery, electronics, automobile manufacturing, tobacco, plastics machinery, electric power, water conservancy, water treatment/environmental protection, municipal engineering, boiler heating, energy, power transmission and distribution and so on.

IC698CHS009 gas turbine electric card

Link Arbitration: The VMIPCI-5565 system is a fiber-optic daisy chain ring as shown in Figure 2. Each transfer is passed from node-to-node until it has gone all the way around the ring and reaches the originating node. Each node retransmits all transfers that it receives except those that it originated. Nodes are allowed to insert transfers between transfers passing through. Interrupt Transfers: The VMIPCI-5565 provides four network interrupts. Any processor can generate an interrupt on any other node on the network. In addition, any processor can generate an interrupt on all nodes on the network with a single register write. In response to this interrupt register write, the sending VMIPCI-5565 issues a special packet over the network, which contains the command strobe, the sender node ID, the destination node ID, and 32 bits of data. When a receiving node detects the proper combination of destination node ID and command strobe, it stores the sender note ID and the data in one of four 127 location-deep FIFOs. The four FIFOs correspond to the four interrupts. Upon storing this information in a FIFO, the receiving node issues an interrupt to the local processor if it has been software-enabled. The 32 bits of data stored in the FIFO is user-definable and typically is treated as an interrupt vector. As part of an interrupt service routine, the local processor reads this information out of the FIFO and acts accordingly.

PCI Initiator/Direct Memory Access (DMA) Capabilities:

The VMIPCI-5565 supports DMA operations. The DMA sequence is initialized by a few control register writes to the VMIPCI-5565 by the host. Therefore, the VMIPCI-5565 becomes a PCI initiator and moves the specified block of data up to 64MB without further host attention. The PCI architecture ensures that the VMIPCI-5565 does not monopolize the PCI bus and causes the VMIPCI-5565’s DMA engine to automatically split large blocks in small bursts. The VMIPCI-5565 can be programmed to issue a PCI interrupt upon completion of DMA process. There are two independent DMA engines, each capable of reading or writing. It is possible for a Read DMA and a Write DMA to occur simultaneously. Error Management: Errors are detected by the VMIPCI-5565 with the use of the error detection facilities of the Fibre Channel encoder/decoder and additional cyclic redundant encoding and checking. When a node detects an error, the erroneous transfer is removed from the system and an interrupt is generated, if enabled.

Protection Against Lost Data:

The product is designed to prevent either FIFO from becoming full and overflowing. It is important to note the only way that data can start to accumulate in FIFOs is for data to enter the node at a rate greater than the network data rate. Since data can enter from the fiber and from the PCI bus, it is possible to exceed these rates. If the transmit FIFO becomes half-full, a bit in the Status Register is set. This is an indication to the node’s software that subsequent WRITEs to the Reflective Memory should be suspended until the FIFO is less than half-full. Once the transmit FIFO is almost full, writes to the Reflective Memory will be acknowledged with a STOP*. No data will be lost. If the receive FIFO is allowed to become almost full, there is a danger the receiver FIFO may overflow resulting in data loss. In order to prevent this situation, all PCI writes will be acknowledged by a STOP* until the receiver FIFO is less than almost full.