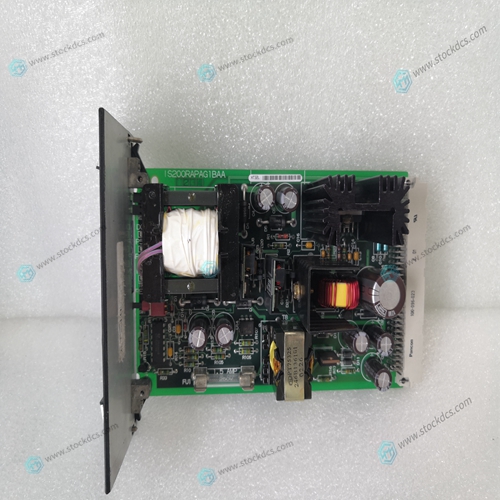

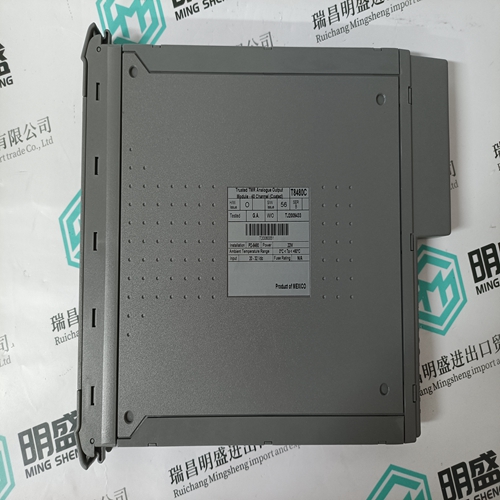

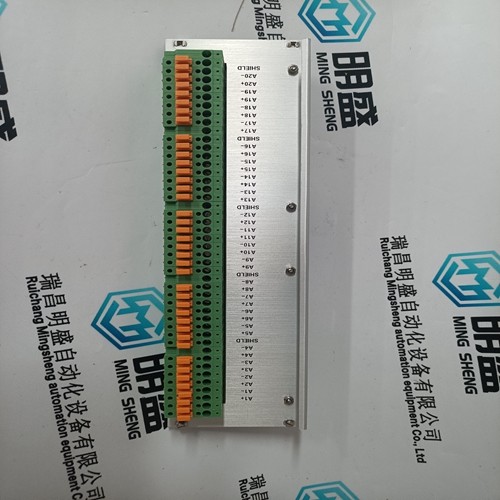

Home > Product > Gas turbine system > GE IS200EHPAG1D Logic sequence module

GE IS200EHPAG1D Logic sequence module

- Product ID: IS200EHPAG1D

- Brand: GE

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:GEIS200EHPAG1DLogic sequence module

- Get the latest price:Click to consult

GE IS200EHPAG1D Logic sequence module

The RDNA driver program runs on the host. The DPP array is the heart of the RDNA processor. The array is organized as a set of workgroup processor pipelines, each independent from the others, that operate in parallel on streams of floating-point or integer data. The workgroup processor pipelines can process data or, through the memory controller, transfer data to, or from, memory. Computation in a workgroup processor pipeline can be made conditional. Outputs written to memory can also be made conditional. When it receives a request, the workgroup processor pipeline loads instructions and data from memory, begins execution, and continues until the end of the kernel. As kernels are running, the RDNA hardware automatically fetches instructions from memory into on-chip caches; RDNA software plays no role in this. RDNA kernels can load data from off-chip memory into on-chip general-purpose registers (GPRs) and caches.

The AMD RDNA devices

can detect floating point exceptions and can generate interrupts. In particular, they detect IEEE floating-point exceptions in hardware; these can be recorded for post-execution analysis. The software interrupts shown in the previous figure from the command processor to the host represent hardware-generated interrupts for signaling commandcompletion and related management functions. The RDNA processor hides memory latency by keeping track of potentially hundreds of workitems in different stages of execution, and by overlapping compute operations with memoryaccess operations.

Program Organization RDNA

kernels are programs executed by the RDNA processor. Conceptually, the kernel is executed independently on every work-item, but in reality the RDNA processor groups 32 or 64 work-items into a wavefront, which executes the kernel on all 32 or 64 work-items in one pass. The RDNA processor consists of: • A scalar ALU, which operates on one value per wavefront (common to all work items). • A vector ALU, which operates on unique values per work-item. • Local data storage, which allows work-items within a workgroup to communicate and share data. • Scalar memory, which can transfer data between SGPRs and memory through a cache. • Vector memory, which can transfer data between VGPRs and memory, including sampling texture maps.

Common problem

We have this product in stock, and we can deliver it to you at any time when you need it badly.

*The warranty period of all products is 1 year, which has passed the professional test certification.

*If you need to order more than one product, please contact us, and we can offer you a discount.

*We only use HDL UPS and other express delivery methods to deliver spare parts.

*If you find that other suppliers offer lower prices for the same products, we are also willing to offer you further discounts based on their prices.

If you have any other questions, please feel free to contact us via email.

*Please let us know if you need any spare parts, we can give you further assistance, and we are waiting for your inquiry.