Home > Product > DCS control system > ABB 26390582-BL DSTK 128 Connect the cable

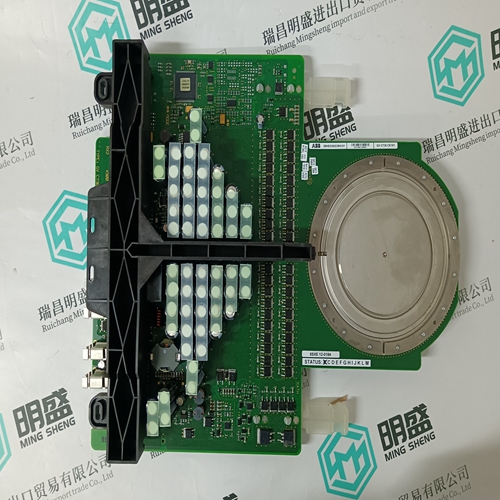

ABB 26390582-BL DSTK 128 Connect the cable

- Product ID: 26390582-BL DSTK 128

- Brand: ABB

- Place of origin: The Swiss

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:xiamen2018@foxmail.com

- Tags:ABB26390582-BLConnect the cableDSTK 128

- Get the latest price:Click to consult

ABB 26390582-BL DSTK 128 Connect the cable

The instruction defines which VGPR(s) supply the addresses for the operation, which VGPRs supply or receive data from the operation, and a series of SGPRs that contain the memory buffer descriptor (V# or T#). Also, MIMG operations supply a texture sampler (S#) from a series of four SGPRs; this sampler defines texel filtering operations to be performed on data read from the image.

Vector-memory (VM) operations transfer data between the VGPRs and buffer objects in memory through the texture cache (TC). Vector means that one or more piece of data is transferred uniquely for every thread in the wavefront, in contrast to scalar memory reads, which transfer only one value that is shared by all threads in the wavefront. Buffer reads have the option of returning data to VGPRs or directly into LDS. Examples of buffer objects are vertex buffers, raw buffers, stream-out buffers, and structured buffers.

Buffer objects support both homogeneous and heterogeneous data

but no filtering of read-data (no samplers). Buffer instructions are divided into two groups: • MUBUF: Untyped buffer objects. ◦ Data format is specified in the resource constant. ◦ Load, store, atomic operations, with or without data format conversion. • MTBUF: Typed buffer objects. ◦ Data format is specified in the instruction. ◦ The only operations are Load and Store, both with data format conversion. Atomic operations take data from VGPRs and combine them arithmetically with data already in memory. Optionally, the value that was in memory before the operation took place can be returned to the shader.

Simplified Buffer Addressing

All VM operations use a buffer resource constant (V#) which is a 128-bit value in SGPRs. This constant is sent to the texture cache when the instruction is executed. This constant defines the address and characteristics of the buffer in memory. Typically, these constants are fetched from memory using scalar memory reads prior to executing VM instructions, but these constants also can be generated within the shader.

Buffer instructions (MTBUF and MUBUF) allow the shader program to read from, and write to, linear buffers in memory. These operations can operate on data as small as one byte, and up to four Dwords per work-item. Atomic arithmetic operations are provided that can operate on the data values in memory and, optionally, return the value that was in memory before the arithmetic operation was performed.

Our superior products

ABB -- AC 800M controller, Bailey, PM866 controller, IGCT silicon controlled 5SHY 3BHB01 3BHEO0 3HNA00 DSOC series

BENTLY --- 3500 system/proximitor, front and rear cards, sensors, power modules, probes, cables

Emerson -- modbus card, power panel, controller, power supply, base, power module, switch

EPRO --- Data acquisition module, probe, speed sensor, vibration sensor, shaft vibration transmitter, proximitor

FOXBORO - thermal resistance input/output module, power module, communication module, cable, controller, switch

GE --- module, air switch, I/O module, display, CPU module, power module, converter, CPU board, Ethernet module, integrated protection device, power module, gas turbine card

HIMA --- DI module, processor module, AI card, pulse encoder

Honeywell --- Secure digital output card, program module, analog input card, CPU module, FIM card

MOOG - servo valve, controller, module, power module

NI --- Information acquisition card, PXI module, card, chassis multi-channel control card

WESTINGHOUSE --- RTD thermal resistance input module, AI/AO/DI/DO module, power module, control module, base module

Woodward - Regulator, module, controller, governor

YOKOGAWA - Servo module, control cabinet node unit