Home > Product > Servo control system > REXROTH HCS02.1E-W0012-A03-NNNN Pulse interface module

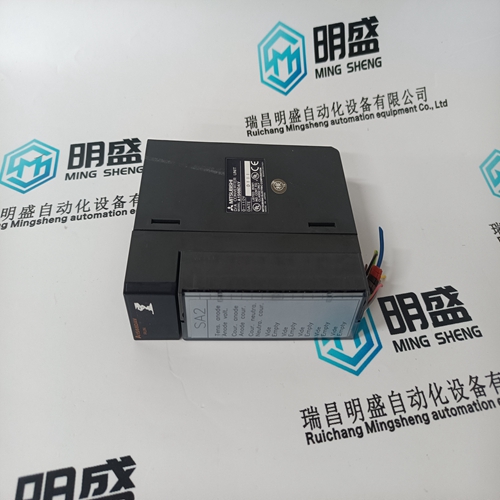

REXROTH HCS02.1E-W0012-A03-NNNN Pulse interface module

- Product ID: HCS02.1E-W0012-A03-NNNN

- Brand: REXROTH

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:xiamen2018@foxmail.com

- Tags:REXROTHHCS02.1E-W0012-A03-NNNNPulse interface module

- Get the latest price:Click to consult

REXROTH HCS02.1E-W0012-A03-NNNN Pulse interface module

The local data bus on the MVME162 is a 32-bit synchronous bus that is based on the MC68040 bus, and which supports burst transfers and snooping. The various local bus master and slave devices use the local bus to communicate. The local bus is arbitrated by priority type arbiter and the priority of the local bus masters from highest to lowest is: 82596CA LAN, NCR 53C710 SCSI, VMEbus, and MPU. Generally speaking, any master can access any slave; however, not all combinations pass the common sense test. Refer to the MVME162 Embedded Controller Programmer’s Reference Guide and to the user’s guide for each device to determine its port size, data bus connection, and any restrictions that apply when accessing the device.

MC68040/MC68LC040 MPU

The MVME162 is equipped with an MC68040 or MC68LC040 microprocessor. The MC68040/MC68LC040 have on-chip instruction and data caches; the MC68040 also provides a floating-point coprocessor. Refer to the M68040 Microprocessor User’s Manual for more information. EPROM and Flash Memory The MVME162 implementation includes four 2-Mbit Flash devices organized in a 256Kbit x 8 configuration. The EPROM location is a standard JEDEC 32- pin PLCC capable of 4 Mbit densities (128 Kbit x 8; 256 Kbit X 8; 512 Kbit x 8; 1 Mbit x8) organized as a 512Kbit x 8 device. A jumper setting (GPIO3, pins 9- 10 on J22) allows reset code to be fetched either from Flash memory (GPIO3 installed) or from the EPROM (GPIO3 removed).

SRAM

The MVME162 provides 512KB of 32-bit-wide onboard static RAM in a single non-interleaved architecture with onboard battery backup. The worst case elapsed time for battery protection is 200 days. Specifics on SRAM performance can be found in the section on the SRAM Memory Controller in the MCchip Programming Model in the MVME162 Embedded Controller Programmer’s Reference Guide. The SRAM arrays are not parity protected. The battery backup function for the MVME162 SRAM is provided by a Dallas DS1210S device that supports primary and secondary power sources. In the event of a main board power failure, the DS1210S checks power sources and switches to the source with the higher voltage

Professional seller

Professional sales of major electrical brand products in the world

Overseas direct purchase of products, authentic inventory, price concessions

After sales warranty, complete models, same products, different prices and services