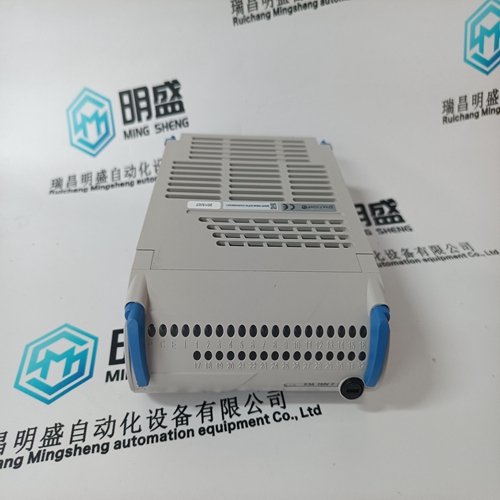

Home > Product > Servo control system > REXROTH HDS02.2-W040N-HS79-01-FW Channel isolation module

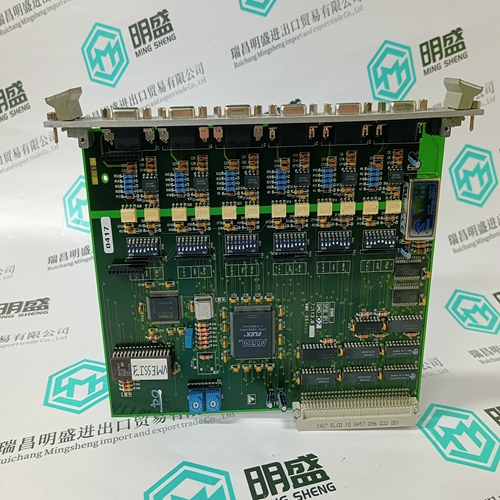

REXROTH HDS02.2-W040N-HS79-01-FW Channel isolation module

- Product ID: HDS02.2-W040N-HS79-01-FW

- Brand: REXROTH

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:REXROTHHDS02.2-W040N-HS79-01-FWChannel isolation module

- Get the latest price:Click to consult

REXROTH HDS02.2-W040N-HS79-01-FW Channel isolation module

When a board is stored, the battery should be disconnected to prolong battery life. This is especially important at high ambient temperatures. The MVME162 is shipped with the battery disconnected (i.e., with VMEbus +5V standby voltage selected as both primary and secondary power source). If you intend to use the battery as a power source, whether primary or secondary, it is necessary to reconfigure the jumpers on J20 before installing the module. Refer to SRAM Backup Power Source Select Header J20 in Chapter 2 for available jumper configurations. The power leads from the battery are exposed on the solder side of the board. The board should not be placed on a conductive surface or stored in a conductive bag unless the battery is removed.Lithium batteries incorporate flammable materials such as lithium and organic solvents. If lithium batteries are mistreated or handled incorrectly, they may burst open and ignite, possible resulting in injury and/or fire.

When dealing with lithium batteries

carefully follow the precautions listed below in order to prevent accidents.

❏ Do not short-circuit.

❏ Do not disassemble, deform, or apply excessive pressure.

❏ Do not heat or incinerate.

❏ Do not apply solder directly.

❏ Do not use different models, or mix new and old batteries together.

❏ Do not charge.

❏ Always check proper polarity. To remove the battery from the module, carefully pull the battery from the socket. Before installing a new battery, ensure that the battery pins are clean. Note the battery polarity and press the battery into the socket. When the battery is in the socket, no soldering is required.

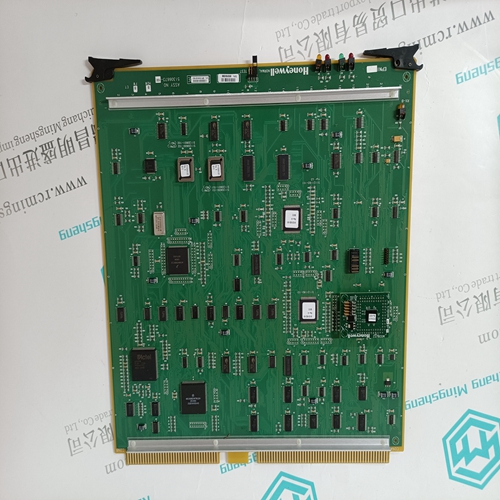

Onboard DRAM

The MVME162 offers a 1MB, a 4MB, and an 8MB DRAM option. The DRAM architecture is non-interleaved for 1MB and interleaved for 4MB and 8MB. Parity protection can be enabled with interrupts or bus exception when a parity error is detected. DRAM performance is specified in the section on the DRAM Memory Controller in the MCchip Programming Model in the MVME162 Embedded Controller Programmer’s Reference Guide. The DRAM map decoder can be programmed to accommodate different base address(es) and sizes of mezzanine boards. The onboard DRAM is disabled by a local bus reset and must be programmed before the DRAM can be accessed. Refer to the MCchip description in the MVME162 Embedded Controller Programmer’s Reference Guide for detailed programming information. Most DRAM devices require some number of access cycles before the DRAMs are fully operational. Normally this requirement is met by the onboard refresh circuitry and normal DRAM initialization. However, software should insure that a minimum of 10 initialization cycles are performed to each bank of RAM.

Professional seller

Professional sales of major electrical brand products in the world

Overseas direct purchase of products, authentic inventory, price concessions

After sales warranty, complete models, same products, different prices and services