Home > Product > PLC programmable module > RELIANCE 45C363 Pulse interface module

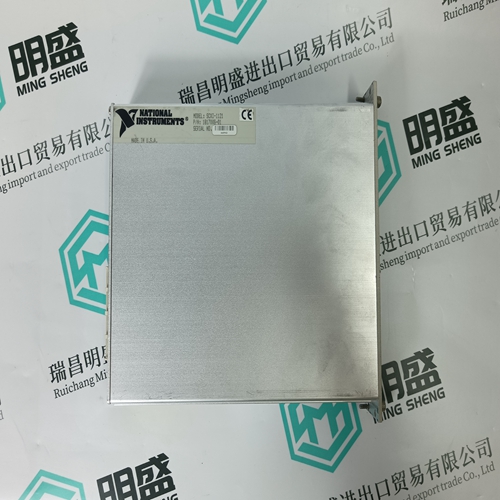

RELIANCE 45C363 Pulse interface module

- Product ID: 45C363

- Brand: Reliance

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:xiamen2018@foxmail.com

- Tags:RELIANCE45C363Pulse interface module

- Get the latest price:Click to consult

RELIANCE 45C363 Pulse interface module

This register allows the VMEbus address and the local address to differ. The value in this register is the base address of the VMEbus resource that is associated with the starting and ending address selection from the previous questions. Default is 0.This register defines which bits of the address are significant. A logical "1" indicates significant address bits, logical "0" is nonsignificant. Default is 0.ENV asks the following series of questions to set up IndustryPack modules (IPs) on MVME172LXs. The MVME172 VME Embedded Controller Programmer’s Reference Guide describes the base addresses and the IP register settings. Refer to that manual for information on setting base addresses and register bits.The IP2 ASIC on the MVME172LX supports up to four IndustryPack (IP) interfaces, designated IP_a through IP_d. The MVME172LX itself accommodates two IPs: IP_a and IP_b. In the following discussion, the segments applicable to IP_c and IP_d are not used in the MVME172LX.

If you have specified environmental

parameters that will cause an overlap condition, a warning message will appear before the environmental parameters are saved in NVRAM. The important information about each configurable element in the memory map is displayed, showing where any overlap conditions exist. This allows you to quickly identify and correct an undesirable configuration before it is saved.This chapter describes the MVME172LX VME embedded controller on a block diagram level. The Description of Features provides an overview of the MVME172LX, followed by a detailed description of several blocks of circuitry. Figure 4-1 shows a block diagram of the overall board architecture. Detailed descriptions of other MVME172LX blocks, including programmable registers in the ASICs and peripheral chips, can be found in the MVME172 Embedded Controller Programmer’s Reference Guide (part number VME172A/PG). Refer to it for a functional description of the MVME172LX in greater depth.

The MVME172LX is based on the MC68060/MC68LC060 microprocessor.

Various versions of the MVME172LX have 4, 8, or 16MB of parity-protected DRAM or 4, 8, 16, 32, or 64MB of ECCprotected DRAM; 128KB of SRAM (with battery backup); time-of-day clock (with battery backup); an optional LAN Ethernet transceiver interface; four serial ports with EIA-232-D interface; six tick timers with watchdog timer(s); two EPROM sockets; 2MB Flash memory (one Flash device); two IndustryPack (IP) interfaces with DMA; optional SCSI bus interface with DMA; and an optional VMEbus interface (local bus to VMEbus/VMEbus to local bus, with A16/A24/A32, D8/D16/D32 bus widths and a VMEbus system controller).

Professional seller

Professional sales of major electrical brand products in the world

Overseas direct purchase of products, authentic inventory, price concessions

After sales warranty, complete models, same products, different prices and services