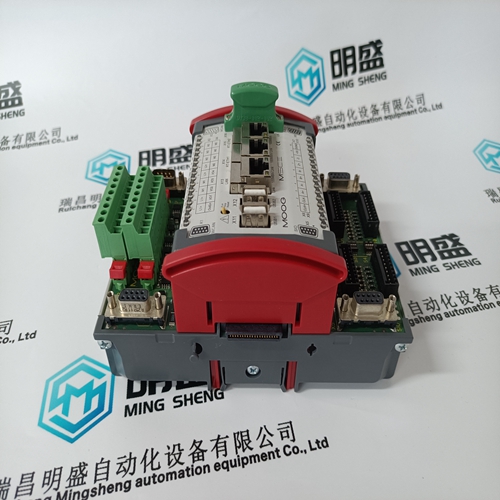

Home > Product > Robot control system > Okuma MIV01A-1-B5 Remote I/O module

Okuma MIV01A-1-B5 Remote I/O module

- Product ID: MIV01A-1-B5

- Brand: OKUMA

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:OkumaMIV01A-1-B5Remote I/O module

- Get the latest price:Click to consult

Okuma MIV01A-1-B5 Remote I/O module

VMEchip2 ASIC Provides the VMEbus interface. The VMEchip2 includes:

❏ Two tick timers

❏ Watchdog timer

❏ Programmable map decoders for the master and slave interfaces, and a VMEbus to/from local bus DMA controller

❏ VMEbus to/from local bus non-DMA programmed access interface

❏ VMEbus interrupter

❏ VMEbus system controller

❏ VMEbus interrupt handler

❏ VMEbus requester

MEMC040 Memory Controller ASIC

The MEMC040 memory controller ASIC provides the programmable interface for the parity-protected DRAM mezzanine board. MCECC Memory Controller ASIC The MCECC memory controller ASIC provides the programmable interface for the ECC-protected DRAM mezzanine board.

The major functional blocks of the MVME187 covered in this section are:

❏ Front panel switches and LED indicators

❏ Data bus structure ❏ M88000 MPU ❏ EPROM ❏ SRAM

❏ Onboard DRAM ❏ Battery backed up RAM and clock

Data Bus Structure

The local data bus on theMVME187 is a 32-bit synchronous bus based on the MC68040 bus, and supports burst transfers and snooping. Local Bus Arbitration The various local bus master and slave devices use the local bus to communicate. The local bus is arbitrated by priority type arbiter and the priority of the local bus masters from highest to lowest is: 1. 82596CA LAN (highest) 2. CD2401 serial (through the PCCchip2) 3. 53C710 SCSI 4. VMEbus 5. MPU (lowest) In general, any master can access any slave; however, not all combinations pass the “common sense test.” Refer to the Single Board Computers Programmer's Reference Guide and to the user's guide for each device to determine its port size, data bus connection, and any restrictions that apply when accessing the device.

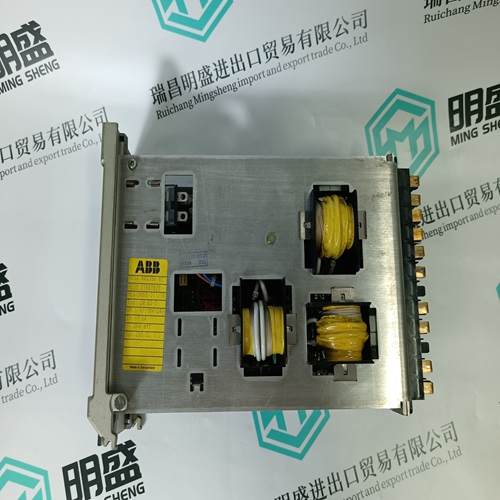

Payment method and delivery

Shipment: EMS,DHL,UPS & FEDEX

Payment: T/T or Western Union

Professional seller

Professional sales of major electrical brand products in the world

Overseas direct purchase of products, authentic inventory, price concessions

After sales warranty, complete models, same products, different prices and services