Home > Product > PLC programmable module > SST SST-PB3-PCU Logic operation module

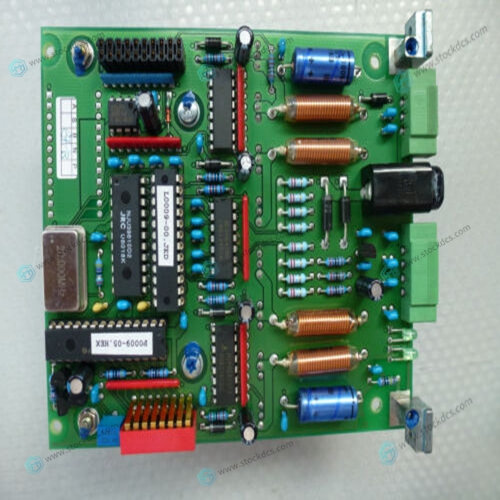

SST SST-PB3-PCU Logic operation module

- Product ID: SST-PB3-PCU

- Brand: SST

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:SSTSST-PB3-PCULogic operation module

- Get the latest price:Click to consult

SST SST-PB3-PCU Logic operation module

Whenever abort is invoked while running target code (a user program), a “snapshot” of the processor state is captured and stored in the target registers. For this reason, abort is most appropriate when terminating a user program that is being debugged. The target IP, register contents, etc., help to pinpoint the malfunction. Abort Sequence Pressing and releasing the ABORT switch does the following: 1. Generates a local board condition which may interrupt the processor if enabled. 2. Displays the target registers on the screen, reflecting the machine state at the time the ABORT switch was pressed. 3. Removes any breakpoints installed in the user code and keeps the breakpoint table intact. 4. Returns control to the debugger. Abort is invoked by pressing and releasing the ABORT switch on the MVME187 front panel. Abort should be used to regain control if the program gets caught in a loop, etc.

A “Break” is generated by pressing

and releasing the BREAK key on the console terminal keyboard. ❏ Break does not generate an interrupt. ❏ The only time break is recognized is when characters are sent or received by the console port. Many times it may be desirable to terminate a debugger command prior to its completion; for example, during the display of a large block of memory. Break allows you to terminate the command.

Break Sequence 1. Removes any breakpoints in your code and keeps the breakpoint table intact. 2. Takes a snapshot of the machine state if the function was entered using SYSCALL. This machine state is then accessible to you for diagnostic purposes.

SYSFAIL* Assertion/Negation

Upon a reset/powerup condition the debugger asserts the VMEbus SYSFAIL* line (refer to the VMEbus specification). SYSFAIL* stays asserted if any of the following has occurred: ❏ Confidence test failure ❏ NVRAM checksum error ❏ NVRAM low battery condition ❏ Local memory configuration status ❏ Self test (if System Mode) has completed with error ❏ MPU clock speed calculation failure After debugger initialization is done and none of the above situations have occurred, the SYSFAIL* line is negated. This indicates to the user or VMEbus masters the state of the debugger. In a multi-computer configuration, other VMEbus masters could view the pertinent control and status registers to determine which CPU is asserting SYSFAIL*. SYSFAIL* assertion/negation is also affected by the ENV command. Refer to Appendix A.

About us

We are professional company and we are expert in this business, we have highly experienced production team, or sales team, or purchase team, we have most advanced production line. We are reputable in the market.

Our products

A company specializes in the sales of module spare parts of global famous brands (DCS system) (robot system) (large servo control system). The company's products include distributed control system (DCS), programmable controller (PLC), MOTOROLA MVME industrial module, industrial control communication converter (Anybus), remote output/input module (RTU), industrial computer (IPC), industrial low screen screen (IPC) HMI SCSI (50, 68, 80Pin) AnyBus (Gateway) has become a global sales enterprise of industrial automation spare parts and components