Home > Product > Servo control system > WOODWARD 5501-376 Signal input card

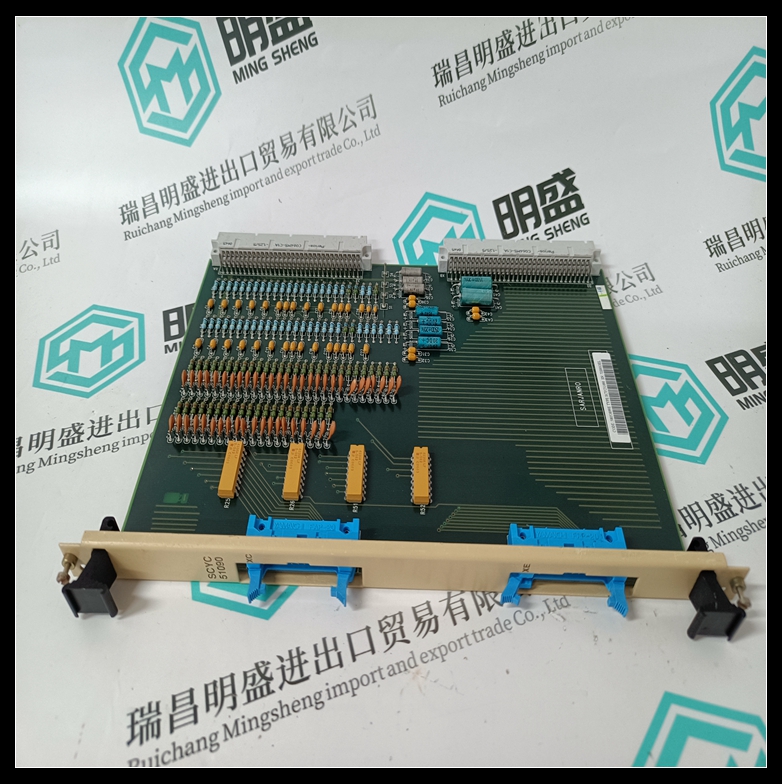

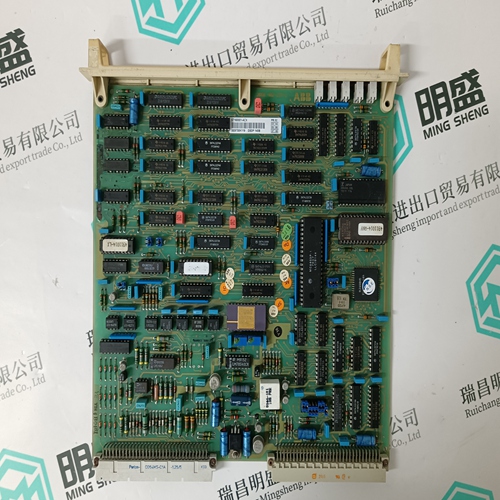

WOODWARD 5501-376 Signal input card

- Product ID: 5501-376

- Brand: WOODWARD

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:xiamen2018@foxmail.com

- Tags:WOODWARD5501-376Signal input card

- Get the latest price:Click to consult

WOODWARD 5501-376 Signal input card

The CLRSWI register is used by the software to clear an SWI interrupt. It is not really a register itself, but it is used to control the clearing of the SWI bits. The state of the SWI bits can be read from the IST register. For every CLRSWI bit that is written as a "l", the corresponding SWI bit is cleared (removing an interrupt request). Every bit written as a ''O" does nothing. This makes each SWI bit individually resettable by writing a "1" to the corresponding bit in the CLRSWI register. Bit assignments are shown in Table 4-5. Because this location is write only, it is unaffected by reset. (However, all SWI bits are cleared by SRST or LRST.)The !STATE register is used to determine the current state of the three interrupt sources that are generated by transitions: ABRT, ACF, and SF. The value returned on read indicates the current state of each signal. Bit assignments are shown in Table 4-6. Because this register reflects the current state of external requests (not latched), it is not affected by reset.

CLRINT Register

The CLRINT register is used to clear the hardware edge-detectors that generate ABRT, ACF, and SF interrupts. The events that caused the interrupt are only transitions from inactive to active. Writing a "1" to a particular bit clears that bit. Another transition from inactive to active must then occur on that edge-detector input for that interrupt request to be re-asserted. For example, if SYSFAIL"' is asserted, a "1" written to the CLRSFI bit sets SF= 0 in the IST register. However, it does not negate SYSFAIL"'. In order to get another SF interrupt, SYSFAIL"' would have to be negated and then re-asserted. Bit assignments are shown in Table 4-7. Because the CLRINT register is write-only, it is not affected by reset. (However, the interrupt request bits (ABRT, ACF, and SF) are cleared by system reset or local reset.)

The status of ABRT

ACF, and SF is indicated in the IST register. These three interrupt requests are generated on the detection of the interrupting condition by a hardware edge-detector. Clearing the interrupt requests by writing to the CLRINT register does not clear the interrupt condition, it merely clears the interrupt request. The !STATE register (described previously) indicates the state of these three interrupting conditions.

About us

We are professional company and we are expert in this business, we have highly experienced production team, or sales team, or purchase team, we have most advanced production line. We are reputable in the market.

Our products

A company specializes in the sales of module spare parts of global famous brands (DCS system) (robot system) (large servo control system). The company's products include distributed control system (DCS), programmable controller (PLC), MOTOROLA MVME industrial module, industrial control communication converter (Anybus), remote output/input module (RTU), industrial computer (IPC), industrial low screen screen (IPC) HMI SCSI (50, 68, 80Pin) AnyBus (Gateway) has become a global sales enterprise of industrial automation spare parts and components