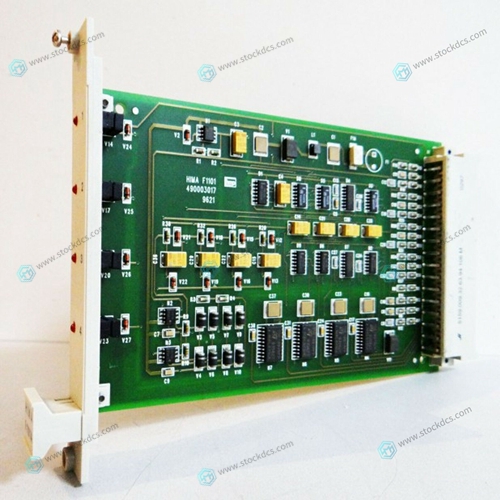

Home > Product > Servo control system > HIMA F1101 Drive input module

HIMA F1101 Drive input module

- Product ID: F1101

- Brand: HIMA

- Place of origin: Germany

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:xiamen2018@foxmail.com

- Tags:HIMAF1101Drive input module

- Get the latest price:Click to consult

HIMA F1101 Drive input module

The GLBRES register is not actually a register; when this location is written to, a SRST is generated. This resets the entire system, including the VMEbus. Note that the VMEbus is reset even if the MVME188A is not system controller.Because the GCSR can be used in configuring and bootstrapping the MVME188A, 12 switches are provided which allow the base address of the GCSR to be located anywhere within the VMEbus A16 address space, as desired. Also, to provide system development flexibility, the switches are accessible through the front panel. The GCSR is the only VMEbus A16 resource on the MVME188A RISC microcomputer.

VMEbus System Controller

The MVME188A RISC microcomputer has a VMEbus system controller which may be enabled by means of a switch accessible through the front panel. Several features are offered by the system controller. A system clock driver within the system controller circuitry drives the VMEbus SYSCLK line with a 16 Mhz clock signal. This signal is not used by ~he MVME188A. When the MVME188A is configured to be system controller, its power monitor is enabled to drive the VMEbus SYSRESET* line. To determine when to assert SYSRESET*, the power monitor reads the VMEbus ACFAIL* line. In addition, the power monitor guarantees that SYSRESET* will be asserted for at least 200 ms after the +5 Vdc line reaches a voltage of +4.75 Vdc.

Timekeeper RAM

The battery backed up SRAM and clock calendar functions provided by the MVME188A are implemented with the MK48T02 Timekeeper RAM. This device offers battery-backed-up operation (up to 11 years if the RTC is off), a clock/calendar function, 2KB of SRAM and circuitry for automatically and safely switching to battery power when system power is removed.As determined by the state of the RONR bit in the UCSR, the arbiter functions either as a PRI or as an RRS arbiter. In the PRI mode, Bus Clear operation is supported; i.e., BCLR* is asserted when a request higher in priority than the current active bus grant level occurs. The arbiter includes a function for generation of a local interrupt following a bus grant timeout. If the arbiter grants the VMEbus to a requester which does not drive BBSY* low within one second, the arbiter withdraws the bus grant and interrupts the local processor. The interrupt acknowledge out (IACKOUT*) line to the local interrupter is driven by the !ACK daisy chain driver whenever IACKIN* is low followed by the assertion of either data strobe

About us

We are professional company and we are expert in this business, we have highly experienced production team, or sales team, or purchase team, we have most advanced production line. We are reputable in the market.

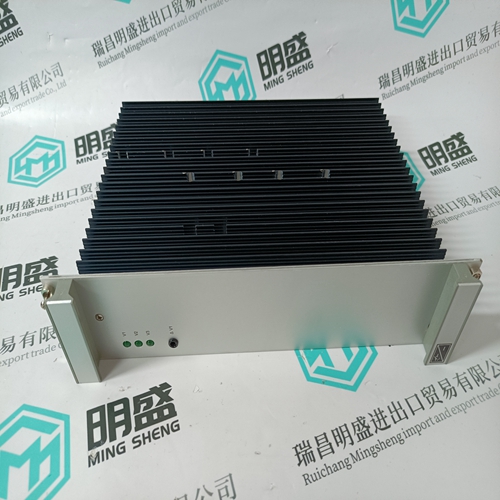

Our products

A company specializes in the sales of module spare parts of global famous brands (DCS system) (robot system) (large servo control system). The company's products include distributed control system (DCS), programmable controller (PLC), MOTOROLA MVME industrial module, industrial control communication converter (Anybus), remote output/input module (RTU), industrial computer (IPC), industrial low screen screen (IPC) HMI SCSI (50, 68, 80Pin) AnyBus (Gateway) has become a global sales enterprise of industrial automation spare parts and components