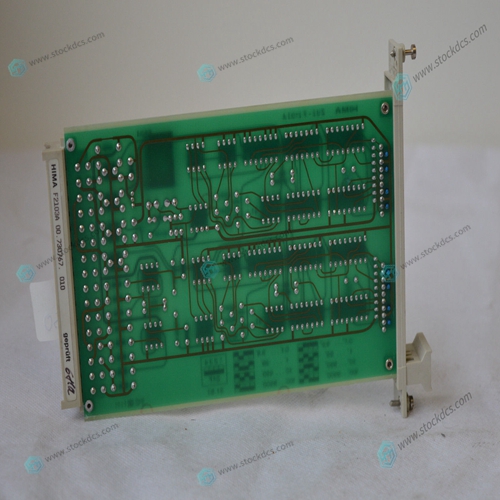

Home > Product > Servo control system > HIMA F2103a Servo signal card

HIMA F2103a Servo signal card

- Product ID: F2103a

- Brand: HIMA

- Place of origin: Germany

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:HIMAF2103aServo signal card

- Get the latest price:Click to consult

HIMA F2103a Servo signal card

Initialize Command The initialize command is set by reading the diagnostic lalclt.. It is exited by reading the CSR. The initialize mode should not be entered unless the memory controller is in the pass through mode with fast refresh enabled. This command will modify the checkbits of each DRAM location so that they will not represent an error condition when accessed in the normal mode. The initialize command takes 131,072,000 clock cycles to complete. This is 5.24 seconds at 25 MHz. Note that the diagnostic latch is a write-only latch. Therefore, reading the latch. to set the initialize commnd does not restrict programming flexibility. This command should be executed before the normal mode is entered.

Refresh Period

CSR bit 0 controls the refresh period. The normal refresh period is 15.4 µ.sec. Setting CSR bit 0 to a one will decrease the refresh period te 1.4 µ.sec. This will reduce the test time of the refresh scrubbing function. Error Counter There is an eight bit counter which is accessable at the CSR.. It will increment when single-bit errors are encountered. The single-bit errors can be a result of refresh or bus access. It does not increment for double-bit errors. It is cleard under CSR control or by reset. Syndrome Bits The CSR has two seven-bit fields which captures the syndrome bits of the last memory read access. The contents are preserved when a single-bit error is detected by the EOC. The syndrome bits will point to the memory device which caused the error. Reading the CSR will re-enable the captures. Kefer to the taWe for syndrome bit encoding in the Am29C660 data sheet.

Parity Detection

All write activity to the module will be checked for correct parity. Parity status is maintained in the CSR. The parity status can be cleared by a power-on reset or by writing a bit to the CSR.The number of wait states required for specific cycle types are indicated in the following table. In the case of refresh, the number indicates dock ticks required to complete the refresh cycle .Note that the two wait states for writes do not affect system performance since the caches requires two wait states for snooping. The performance parameters are for isolated cycles. Since the memory cycles are write posted, a second consecutive write cycle would require an additional three ticks. The seven ticks for refresh includes the RAS pre-charge time required for the pending cycle.

About us

We are professional company and we are expert in this business, we have highly experienced production team, or sales team, or purchase team, we have most advanced production line. We are reputable in the market.

Our products

A company specializes in the sales of module spare parts of global famous brands (DCS system) (robot system) (large servo control system). The company's products include distributed control system (DCS), programmable controller (PLC), MOTOROLA MVME industrial module, industrial control communication converter (Anybus), remote output/input module (RTU), industrial computer (IPC), industrial low screen screen (IPC) HMI SCSI (50, 68, 80Pin) AnyBus (Gateway) has become a global sales enterprise of industrial automation spare parts and components