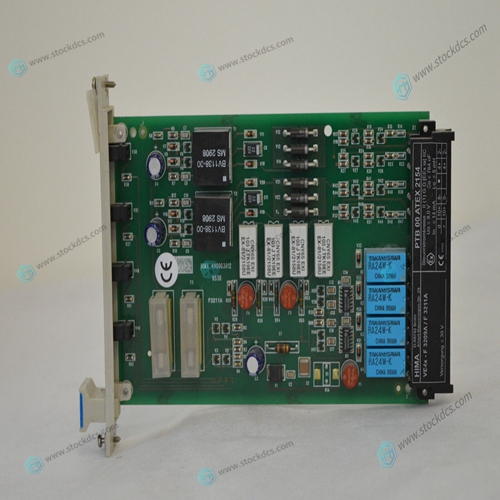

Home > Product > Servo control system > HIMA F3211A Drive output module

HIMA F3211A Drive output module

- Product ID: F3211A

- Brand: HIMA

- Place of origin: Germany

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:HIMAF3211ADrive output module

- Get the latest price:Click to consult

HIMA F3211A Drive output module

The address and data paths used to access the WV AD register are the same as the ones used by the decoder when it is enabled. Consequently, the VADV bit in the CCSR MUST BE CLEAR before any write to the WV AD register. If V ADV is not clear, multiple data and address path buffers are simultaneously active on the same lines. This results in erroneous data being written to the WV AD register; it may also result in damage to the hardware. Because it is write-only, the WV AD register is unaffected by SRST or LRST.There is only one register for holding the page address to the VMEbus address decoder S:RAM. A write to the WV AD register will change the location (page address) that the RVAD register accesses and vice-versa.

RVAD Register

The read VMEbus address decoder register is used to verify the configuration of the MVME188A VMEbus slave address map. It is read/write; on read it returns the code for the address space mapped to that page (lower 2 data bits); the upper 30 bits are always "l". On write, an address (VPN[9:0]) and a map select bit (V ASP) are written to the upper bits of the RV AD register; the address is used on a subsequent read as a page address in the map corresponding to the V ASP bit. Bit assignments are shown in Table 4-39. The address and data paths used to access the RV AD register are the same as the ones used by the decoder when it is enabled. Consequently, the V ADV bit in the CCSR MUST BE CLEAR before any READ or WRITE to the RV AD register. If V ADV is not clear, multiple data and address path buffers will be simultaneously active on the same lines. This will result in erroneous data being written to or read from the RV AD register; it may also result in damage to the hardware.

Because there is only one address register

if the last write to the WV AD is a write of a page you wish to verify, it is not necessary to write to the RV AD; simply read from the RV AD. The address is loaded by the WV AD write, making a write to RVAD unnecessary. Note that in a multi-CPU environment, protocol should allow only one CPU at a time to access the RV AD/WV AD registers. This prevents the occurrence of the above-mentioned "interleaved writes" while configuring or verifying the contents of the VMEbus address mapper.

On write, VPN[9:0] is supplied by the M bus master on data bits 31:22, and is written into the read VMEbus address decoder (RVAD) register. On read, these bits are always "1". Note that the address decoder map is never modified by a write to this register (it is modified by writes to the WVAD register).

About us

We are professional company and we are expert in this business, we have highly experienced production team, or sales team, or purchase team, we have most advanced production line. We are reputable in the market.

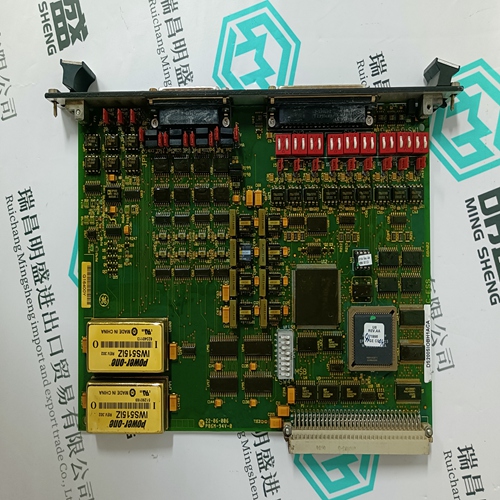

Our products

A company specializes in the sales of module spare parts of global famous brands (DCS system) (robot system) (large servo control system). The company's products include distributed control system (DCS), programmable controller (PLC), MOTOROLA MVME industrial module, industrial control communication converter (Anybus), remote output/input module (RTU), industrial computer (IPC), industrial low screen screen (IPC) HMI SCSI (50, 68, 80Pin) AnyBus (Gateway) has become a global sales enterprise of industrial automation spare parts and components