Home > Product > DCS control system > TRICONEX 4118 Logic control module

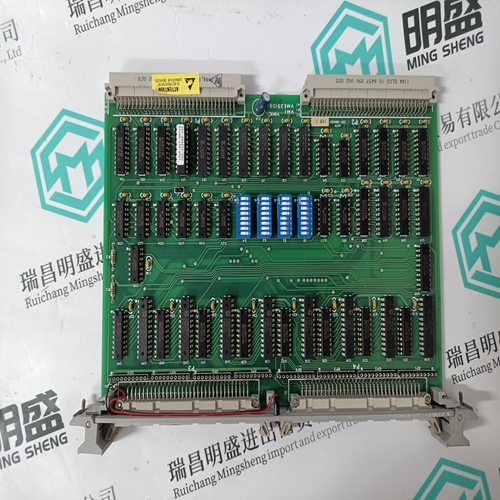

TRICONEX 4118 Logic control module

- Product ID: 4118

- Brand: TRICONEX

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:TRICONEX4118Logic control module

- Get the latest price:Click to consult

TRICONEX 4118 Logic control module

The three interrupt FIFOs are 512 bytes deep so up to 512 interrupts of any level may be queued in the FIFO. A clear function is executed upon a Write to the int ID Register so an interrupt level that has been masked off for some time and contains many global or local interrupts previously sent may be cleared out without servicing them. Only new interrupts received will be serviced. Since the interrupts originally go through the same receive FIFO as data, all data sent before the interrupt will be present in the local node’s memory before the interrupt is issued to the local node.This register contains the node ID of the node to receive the interrupt sent by writing the command register. This register must be set at the same time by using a 16-bit word write to both command register and command node or prior to writing the command register.

INTERRUPT SENDER ID REGISTERS

The three interrupt sender ID registers contain the ID of the node which originated the interrupt currently being serviced. All data sent across the fiber-optic link is tagged with the ID of the originating node so it may be removed from the link once it has been passed around the link one time. The ID is stored in the appropriate register if the data word received is an interrupt. As part of the interrupt handler software, the user must read the appropriate ID register in order to re-arm the currently used interrupt. This process insures that all interrupts sent to the node will be processed. The user may or may not use the ID but it must be read as part of the interrupt handler process. In the event that a certain interrupt has been masked off at the BIM, the FIFO for that interrupt may be cleared by writing to the ID register for the specific interrupt level before the BIM is armed. The ID write process is to be done in addition to the BIM arming process. In the interrupt handling sequence, the user should do only one read per interrupt cycle. Erroneous results will be caused by multiple reads.

LOCAL STATUS INTERRUPT

The fourth interrupt on the MC68153 (INT0) is dedicated to generate an interrupt in the event that the local FIFOs become half-full or a corrupt transfer has been received. If the interrupt is not disabled, every time the local VMIVME-5576 is written to and the transmit FIFO is over half full or a transfer error occurs, an INT0 will be generated. The half-full information flag is also available by looking at the CSR. If the transmit FIFO is allowed to become full and the FIFO half full is set, a BERR will be generated when a Write is attempted to the VMIVME-5576. Tables 4.9-1 and 4.9-2 show the architecture of MC68153 registers. The corrupt transfer interrupt may be masked off by removing the mask jumper. This is done so the user will not be bothered by interrupts in redundant transfer mode.

Superior products

Main products include DCS control system spare parts, PLC system spare parts and robot system spare parts,Advantage brands: Allen Bradley, BentlyNevada, ABB, Emerson Ovation, Honeywell DCS, Rockwell ICS Triplex, B&R, FOXBORO, Schneider PLC, GE Fanuc, Motorola, HIMA, TRICONEX, Prosoft and other imported industrial parts

Application industry

Our main products are widely used in metallurgy, oil and gas, glass manufacturing, aluminum, petrochemical, coal mine, paper making and printing, textile printing and dyeing, machinery, electronic manufacturing, automobile manufacturing, tobacco, plastic machinery, electricity, water conservancy, water treatment/environmental protection, municipal engineering, boiler heating, energy, power transmission and distribution, etc.