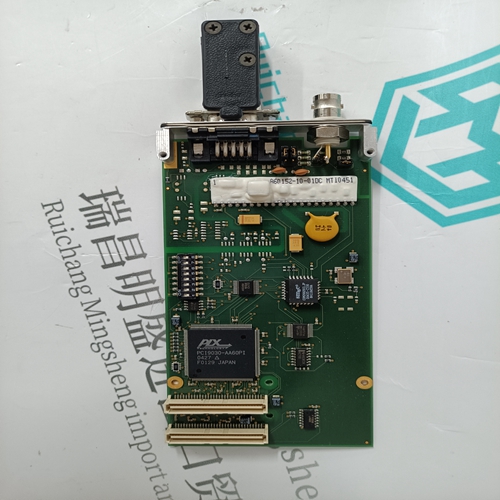

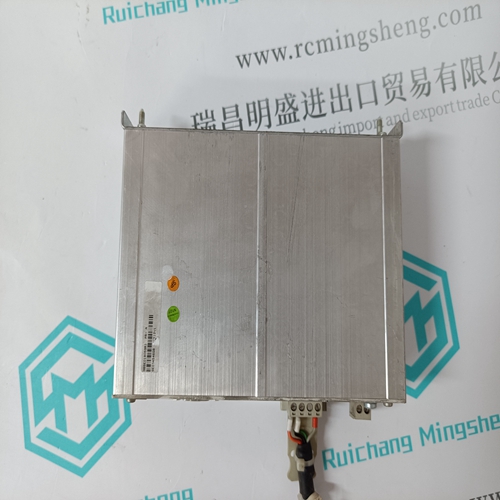

Home > Product > PLC programmable module > SIMENS QLCAMAAN Pulse input card

SIMENS QLCAMAAN Pulse input card

- Product ID: QLCAMAAN

- Brand: SIMENS

- Place of origin: The United States

- Goods status: new/used

- Delivery date: stock

- The quality assurance period: 365 days

- Phone/WhatsApp/WeChat:+86 15270269218

- Email:stodcdcs@gmail.com

- Tags:SIMENSQLCAMAANPulse input card

- Get the latest price:Click to consult

SIMENS QLCAMAAN Pulse input card

Before starting the AD conversion, the minimum signal acquisition time should be met for the selected analog input signal. The signal acquisition time (TACQ) of ADC in PMC234/PMS234 series is fixed to one clock period of ADCLK, the selection of ADCLK must be met the minimum signal acquisition time.

Select the ADC bit resolution

The ADC resolution is 12-bit, please configure adcm register bit [7:5] to be “100” before starting AD conversion via $ADCM instruction. Higher resolution can detect small signal variation; however, it will take more time to convert the analog signal to digital signal. The selection can be done via adcm register. The ADC bit resolution should be configured before starting the AD conversion.

ADC clock selection

The clock of ADC module (ADCLK) can be selected by adcm register; there are 8 possible options for ADCLK from sysclk/1 to sysclk/128. Due to the signal acquisition time TACQ is one clock period of ADCLK, the ADCLK must meet that requirement. The recommended ADC clock is to operate at 2us.

Application industry

The products can be used in the following industries: power plant, paper making, steel, mining, rubber, water supply, cement, chemical industry, glass, printing

Textile, machinery, plastics, coatings, medicine, hospitals, food, hotels, scientific research institutions

This article from the temporal Ming sheng automation equipment co., LTD., reproduced please attach this link: http://www.stockdcs.com/